# EE 330 Lecture 29

**Bipolar Processes**

- Device Sizes

- Parasitic Devices

- JFET

- Thyristors

Thyristors

• SCR – Basic operation

## Exam Schedule

Exam 2 will be given on Friday March 11 Exam 3 will be given on Friday April 15

As a courtesy to fellow classmates, TAs, and the instructor

Wearing of masks during lectures and in the laboratories for this course would be appreciated irrespective of vaccination status

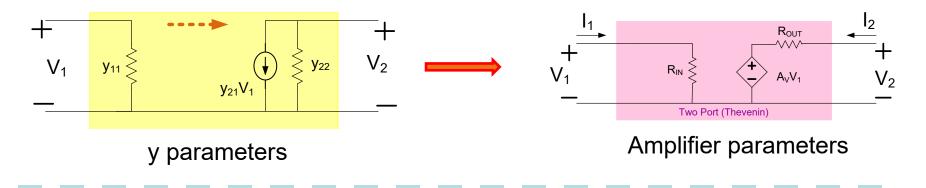

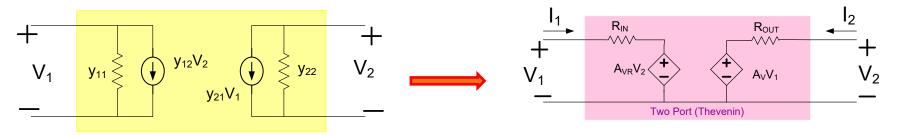

#### Review From Previous Lecture Two-port representation of amplifiers

- Amplifier often unilateral (signal propagates in only one direction: wlog y<sub>12</sub>=0)

- One terminal is often common

- "Amplifier" parameters often used

- Amplifier parameters can also be used if not unilateral

- One terminal is often common

y parameters

Amplifier parameters

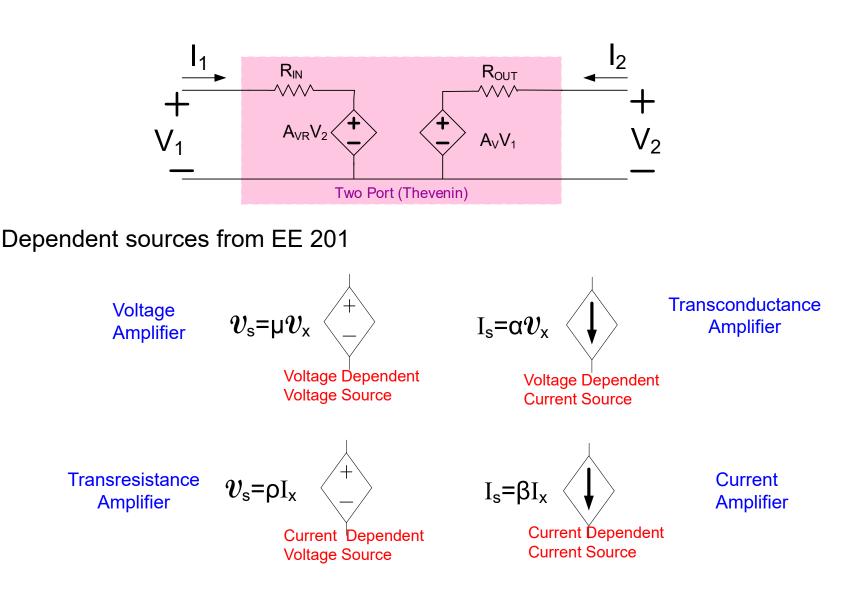

## Relationship with Dependent Sources ?

## **Topical Coverage Change**

Will have several additional lectures on amplifier structures but will temporarily suspend discussion of amplifiers to consider Thyristors

This is being done to get ready for the Thyristor laboratory experiments

## Outline

**Bipolar Processes**

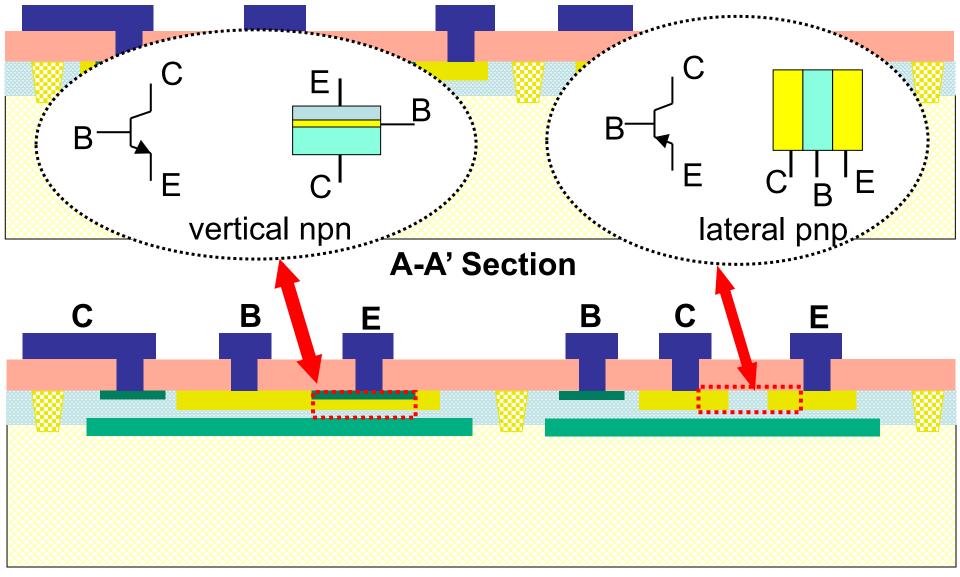

- Parasitic Devices in CMOS Processes

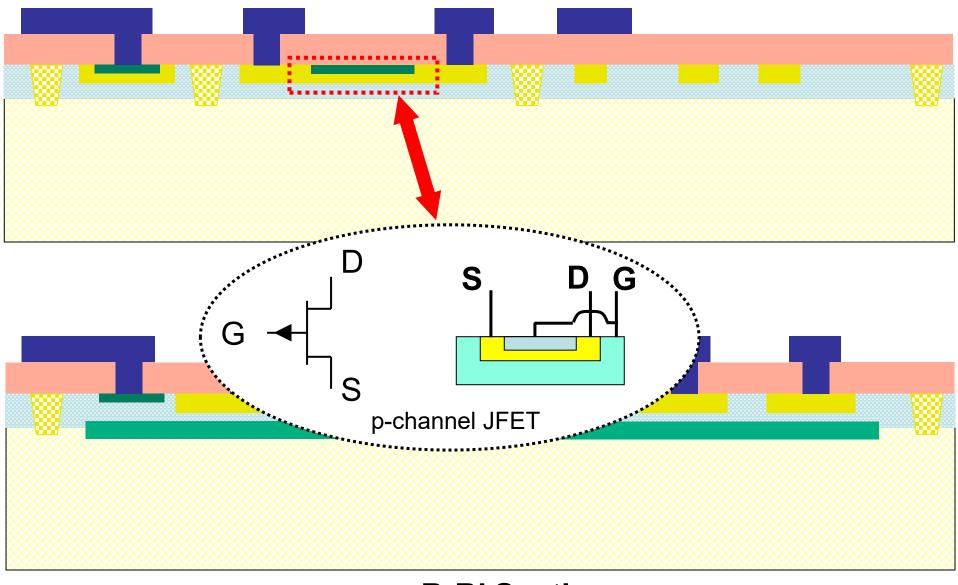

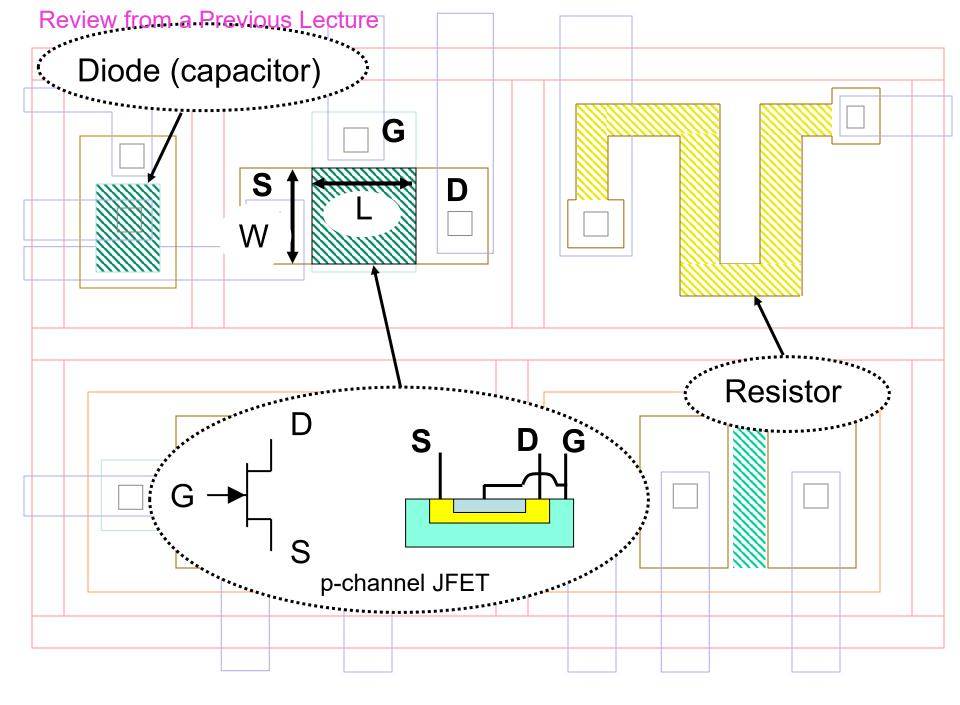

- JFET

- Other Junction Devices

**Special Bipolar Processes**

Thyristors

SCR

TRIAC

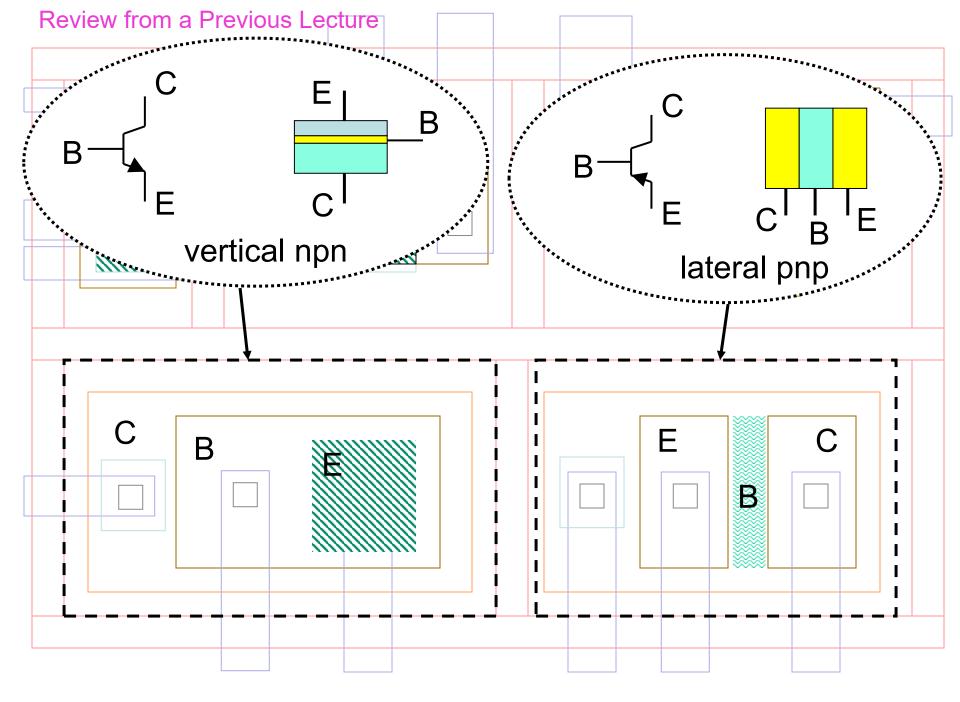

#### **Review from a Previous Lecture**

#### **B-B' Section**

#### **Review from a Previous Lecture**

#### **B-B' Section**

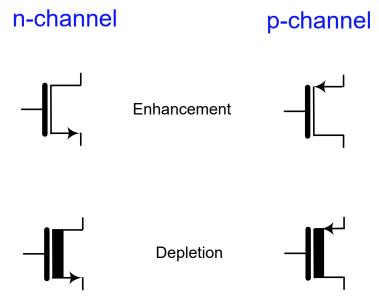

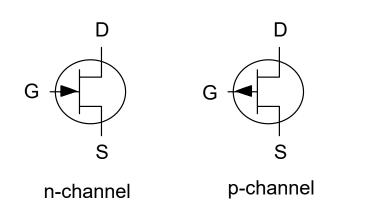

Will consider next the JFET but first some additional information about MOS Devices Enhancement and Depletion MOS Devices

- Enhancement Mode n-channel devices  $V_T > 0$

- Enhancement Mode p-channel devices

V<sub>T</sub> < 0</li>

- Depletion Mode n-channel devices

V<sub>T</sub> < 0</li>

- Depletion Mode p-channel devices

V<sub>T</sub> > 0

## Enhancement and Depletion MOS Devices

- Depletion mode devices require only one additional mask step

- Older n-mos and p-mos processes usually had a depletion device and an enhancement device

- Depletion devices usually not available in CMOS because applications usually do not justify the small increasing costs in processing

- The threshold voltage of either n-channel or p-channel devices is adjusted to a desired value by doing a channel implant before gate oxide is applied

# Outline

**Bipolar Processes**

- Parasitic Devices in CMOS Processes

JFET

- Other Junction Devices

**Special Bipolar Processes**

Thyristors

SCR

TRIAC

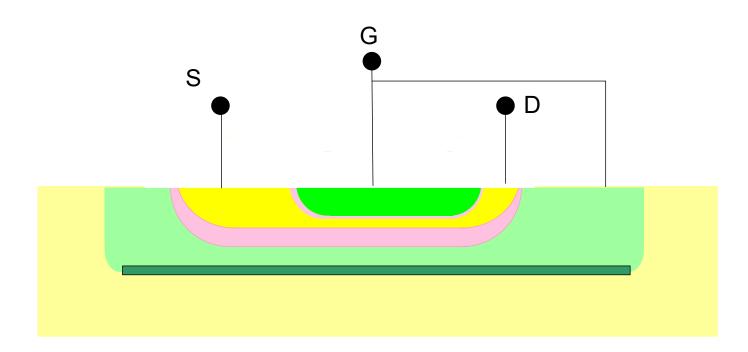

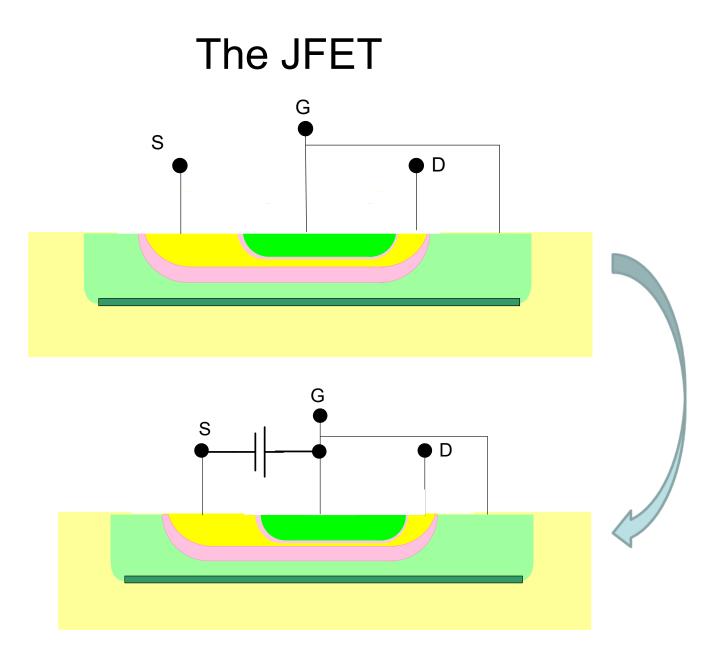

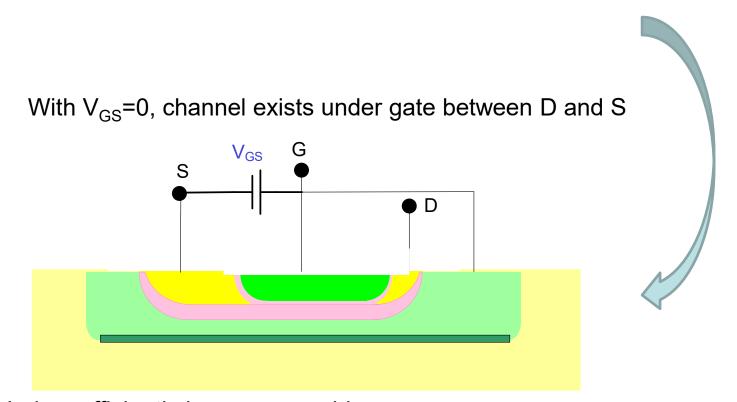

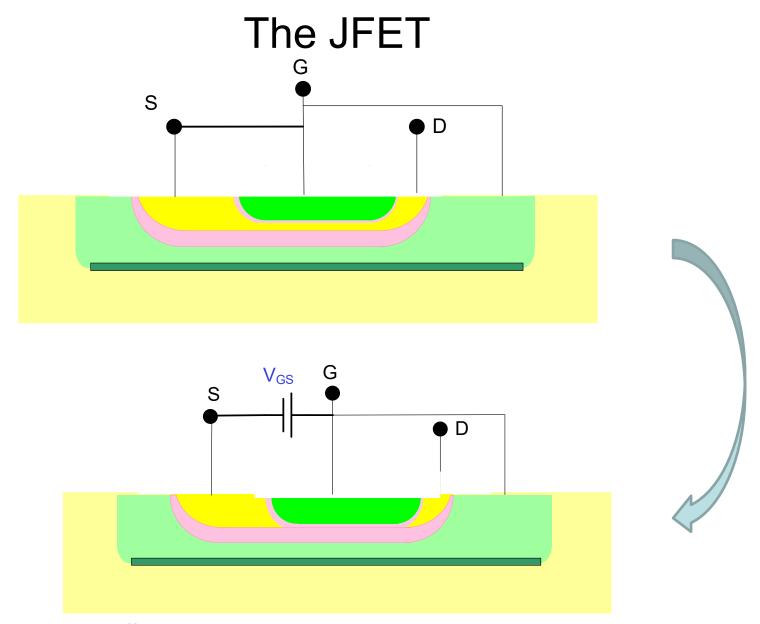

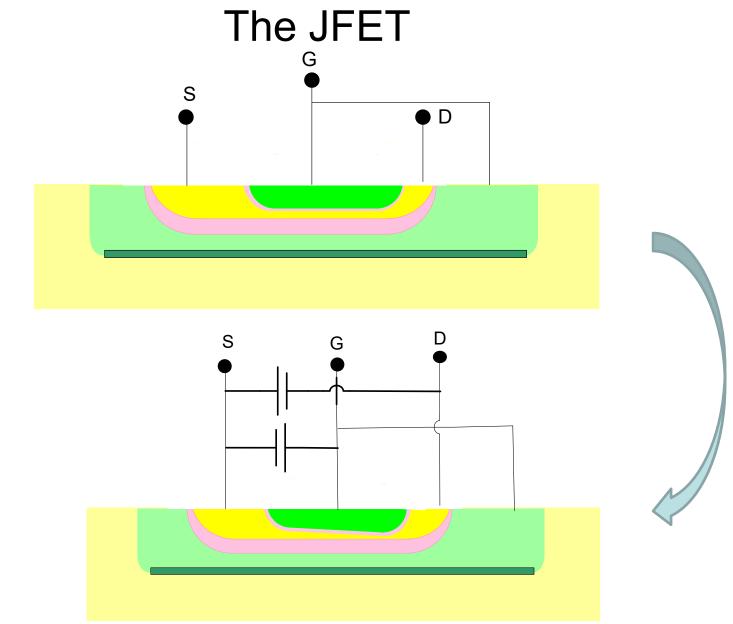

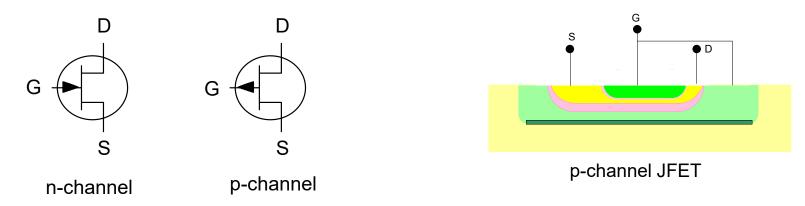

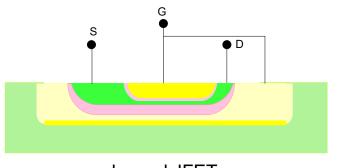

#### The JFET

- Gate is both above and below channel

- With no bias, channel exists between D and S

#### The JFET

#### With $V_{GS}$ =0, channel exists under gate between D and S

Under small reverse bias (depletion region widens and channel thins)

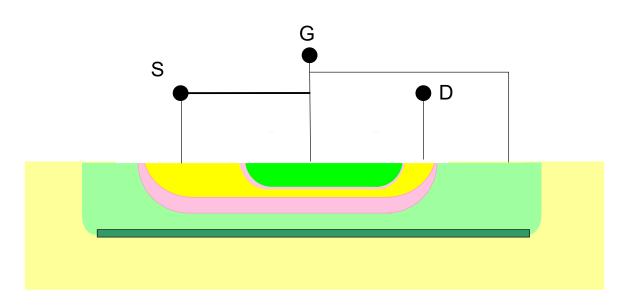

#### The JFET

Under sufficiently large reverse bias (depletion region widens and channel disappears - "pinches off")

Under sufficiently large reverse bias (depletion region widens and channel disappears - "pinches off")

Under small reverse bias and large negative V<sub>DS</sub> (channel pinches off)

#### The JFET

Square-law model of p-channel JFET

$$I_{D} = \begin{cases} 0 & V_{GS} > V_{P} \\ \frac{2I_{DSSp}}{V_{P}^{2}} \left(V_{GS} - V_{P} - \frac{V_{DS}}{2}\right) V_{DS} & -0.3 < V_{GS} < V_{P} & V_{GS} + 0.3 > V_{DS} > V_{GS} - V_{P} \\ I_{DSSp} \left(1 - \frac{V_{GS}}{V_{P}}\right)^{2} & -0.3 < V_{GS} < V_{P} & V_{DS} < V_{GS} - V_{P} \end{cases}$$

(I<sub>DSSp</sub> carries negative sign)

- Functionally identical to the square-law model of MOSFET

- Parameters  $I_{DSS}$  and  $V_P$  characterize the device

- I<sub>DSS</sub> proportional to W/L where W and L are width and length of n+ diff

- V<sub>P</sub> is negative for n-channel device, positive for p-channel device thus JFET is depletion mode device

- Must not forward bias GS junction by over about 300mV or excessive base current will flow (red constraint)

- Widely used as input stage for bipolar op amps

### The JFET

n-channel JFET (not available in this process)

Square-law model of n-channel JFET

$I_{D} = \begin{cases} 0 & V_{GS} < V_{P} \\ \frac{2I_{DSS}}{V_{P}^{2}} \left(V_{GS} - V_{P} - \frac{V_{DS}}{2}\right) V_{DS} & 0.3 > V_{GS} > V_{P} & V_{GS} - 0.3 < V_{DS} < V_{GS} - V_{P} \\ I_{DSS} \left(1 - \frac{V_{GS}}{V_{P}}\right)^{2} & 0.3 > V_{GS} > V_{P} & V_{DS} > V_{GS} - V_{P} \end{cases}$

- Functionally identical to the square-law model of MOSFET

- Parameters I<sub>DSS</sub> and V<sub>P</sub> characterize the device

- I<sub>DSS</sub> proportional to W/L where W and L are width and length of n+ diff

- V<sub>P</sub> is negative for n-channel device, positive for p-channel device thus JFET is depletion mode device

- Must not forward bias GS junction by over about 300mV or excessive base current will flow (red constraint)

- Widely used as input stage for bipolar op amps

# Outline

**Bipolar Processes**

- Parasitic Devices in CMOS Processes

- JFET

**Other Junction Devices**

**Special Bipolar Processes**

Thyristors

SCR

TRIAC

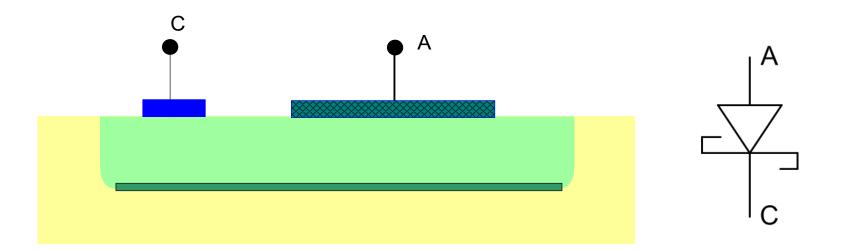

### The Schottky Diode

- Metal-Semiconductor Junction

- · One contact is ohmic, other is rectifying

- Not available in all processes

- Relatively inexpensive adder in some processes

- Lower cut-in voltage than pn junction diode

- High speed

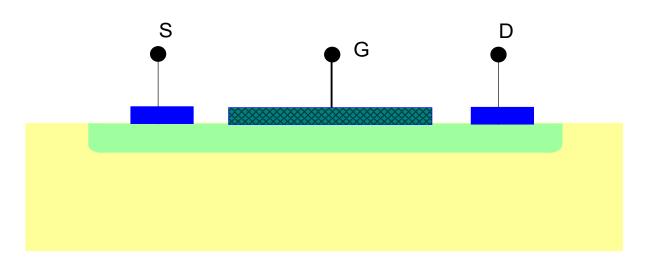

### The MESFET

- Metal-Semiconductor Junction for Gate

- Drain and Source contacts ohmic, other is rectifying

- Usually not available in standard CMOS processes

- Must not forward bias very much

- Lower cut-in voltage than pn junction diode

- High speed

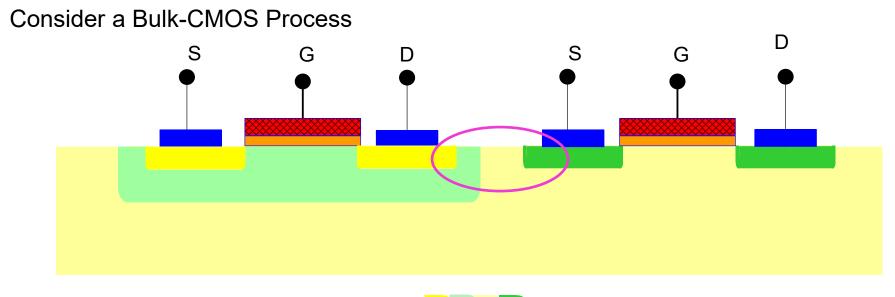

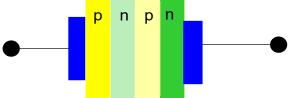

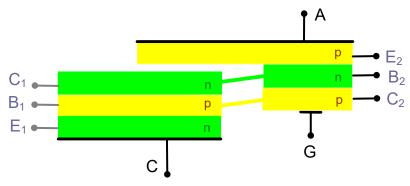

## The Thyristor

A bipolar device in CMOS Processes

Have formed a lateral pnpn device !

Will spend some time studying pnpn devices

# Outline

**Bipolar Processes**

- Parasitic Devices in CMOS Processes

- JFET

- Other Junction Devices

- **Special Bipolar Processes**

# Thyristors

### The good and the bad!

# Thyristors

## The good SCRs Triacs

The bad

Parasitic Device that can destroy integrated circuits

## Outline

**Bipolar Processes**

- Parasitic Devices in CMOS Processes

- JFET

- Other Junction Devices

- **Special Bipolar Processes**

- Thyristors

SCR

TRIAC

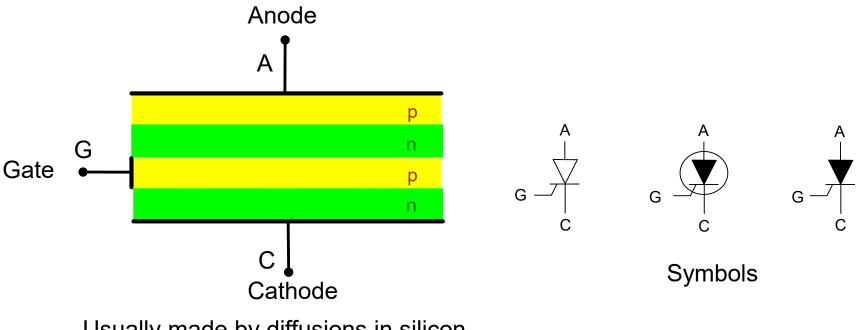

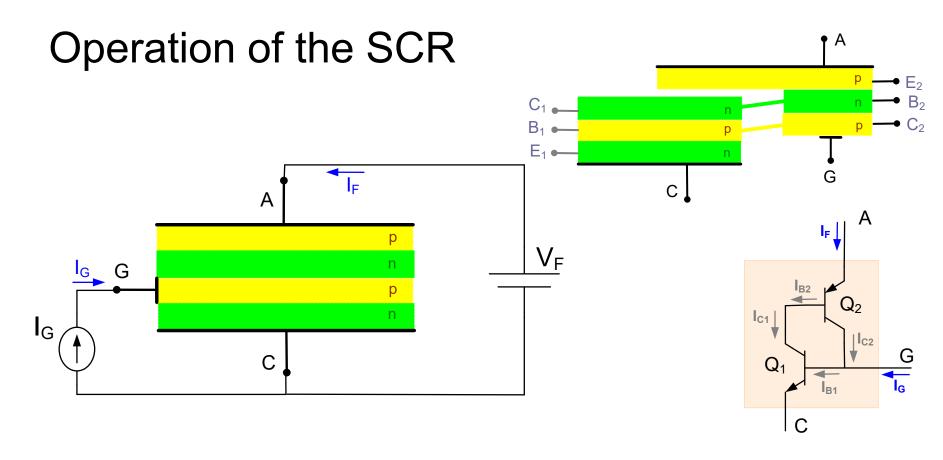

## The SCR

#### Silicon Controlled Rectifier

- Widely used to switch large resistive or inductive loads

- Widely used in the power electronics field

- Widely used in consumer electronic to interface between logic and power

Usually made by diffusions in silicon

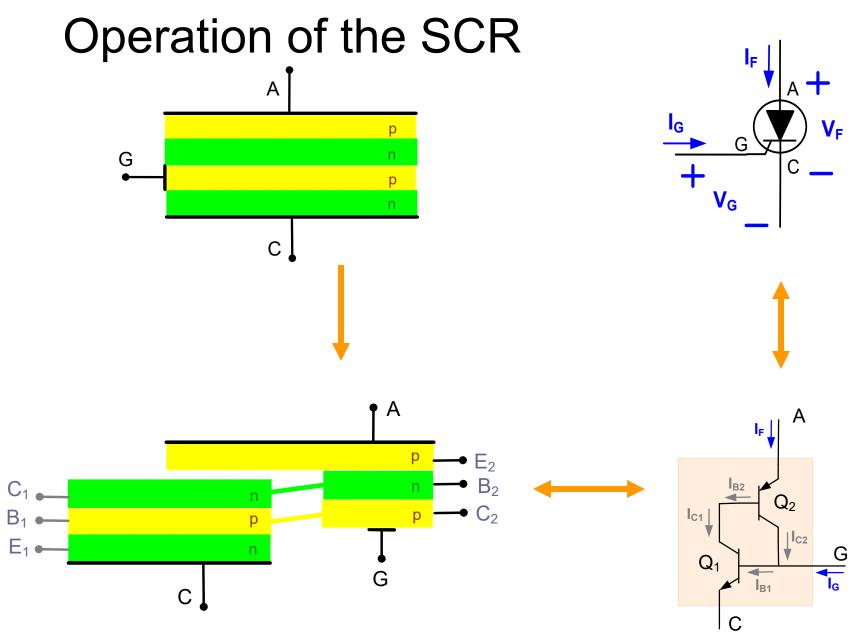

Consider first how this 4-layer 3-junction device operates

Not actually separated but useful for describing operation

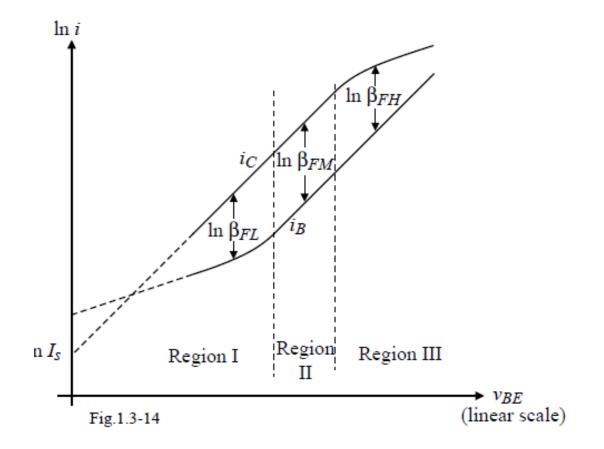

#### Variation of Current Gain ( $\beta$ ) with Bias for BJT

Note that current gain gets very small at low base current levels

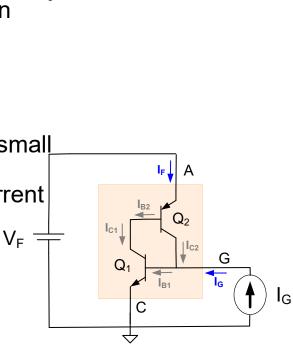

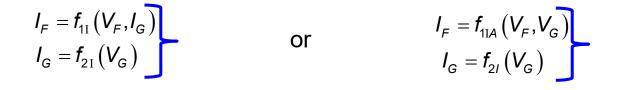

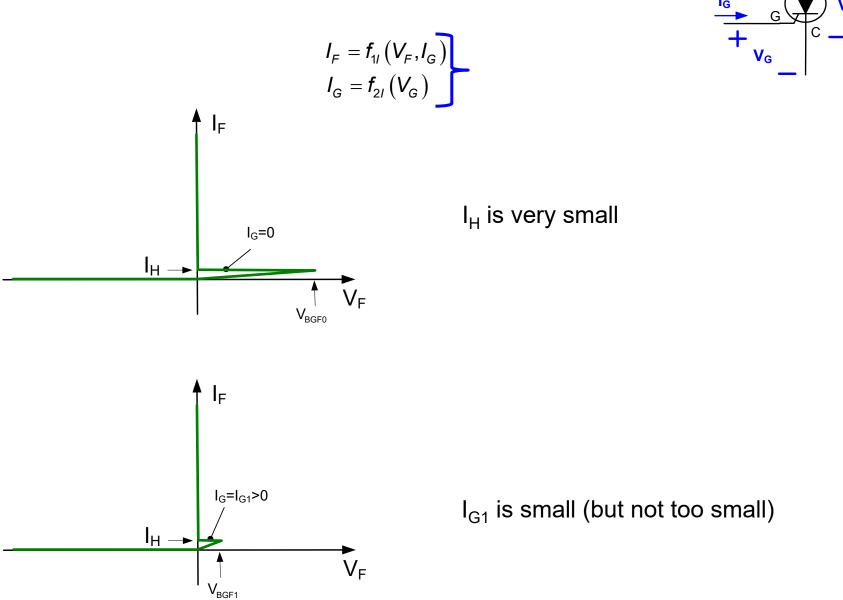

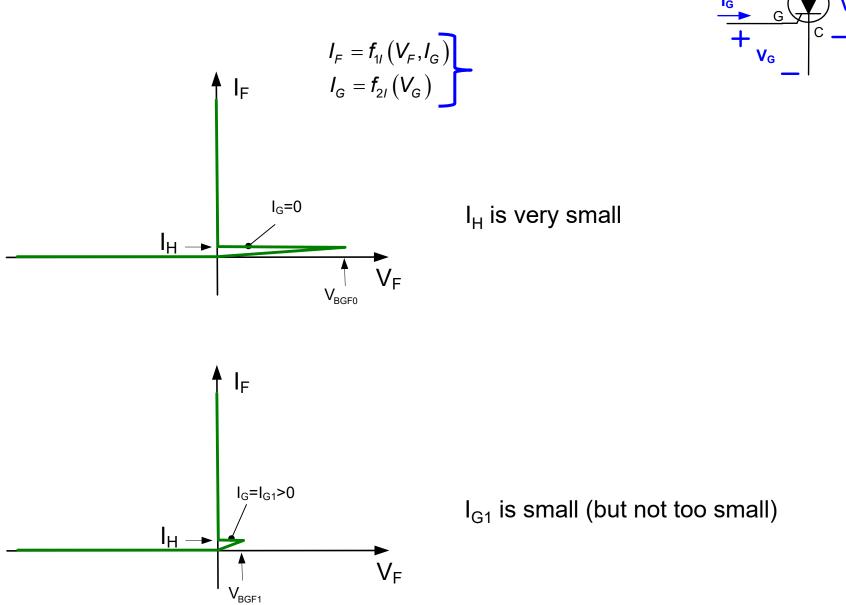

Consider a small positive bias (voltage or current) on the gate (V\_{GC}<0.5V) and a positive and large voltage  $V_{\rm F}$

Will have  $V_{C1} \ge V_F - 0.5V$

Thus Q<sub>1</sub> has a large positive voltage on its collector

Since  $VB_{E1}$  is small,  $I_{C1}$  will be small as will  $I_{C2}$  so diode equation governs BE junction of  $Q_1$   $I_F$  will be very small

Now let bias on the gate increase (V<sub>GC</sub> around 0.6V) so Q<sub>1</sub> and Q<sub>2</sub> in FA  $V_{C1} \ge V_{F}$ - 0.5V

From diode equation, base voltage  $V_{BE1}$  will increase and collector current  $I_{C1}$  will increase Thus base current  $I_{B2}$  will increase as will the collector current of  $I_{C2}$

Under assumption of operation in FA region get expression

$$_{31} = \mathbf{I}_{G} + \beta_{1}\beta_{2}\mathbf{I}_{B1}$$

This is regenerative feedback (actually can show pole in RHP)

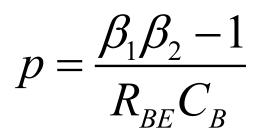

#### Very Approximate Analysis Showing RHP Pole

$$V_G = I_G \frac{R_{BE}}{sR_{BE}C_B + 1 - \beta_1\beta_2}$$

$$V_G s C_B + I_{B1} = I_{C2} + I_G$$

$$I_{C2} = \beta_1 \beta_2 I_{B1}$$

$$I_{B1} R_{BE} = V_G$$

$V_{\text{C1}} \cong V_{\text{F}}\text{-}0.6V$

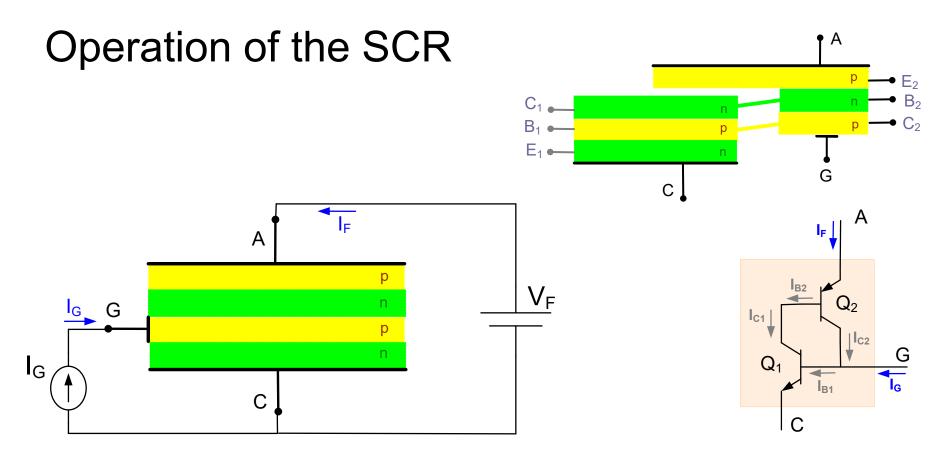

Under assumption of operation in FA region get expression

$\mathbf{I}_{B1} = \mathbf{I}_{G} + \beta_{1}\beta_{2}\mathbf{I}_{B1}$

#### What will happen with this is regenerative feedback?

If  $I_G$  is small (and thus  $\beta_1$  and  $\beta_2$  are small)  $I_F$  will be very small

If  $I_G$  larger but less than  $\beta_1\beta_2I_{B1}$  it can be removed and current will continue to flow

$I_{C1}$  will continue to increase and drive  $Q_1$  into SAT

This will try to drive  $V_A$  towards 0.9V (but forced to be  $V_F$ !)

The current in V<sub>F</sub> will go towards  $\infty$

The SCR will self-destruct because of excessive heating !

Too bad the circuit self-destructed because the small gate current was able to control a lot of current!

E₁

С

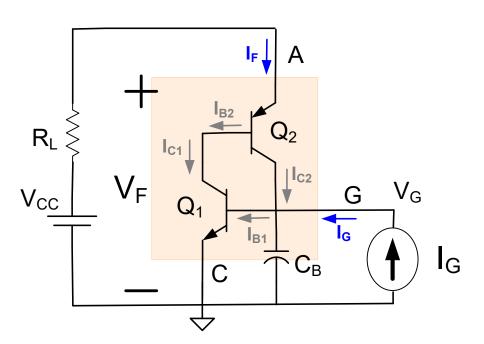

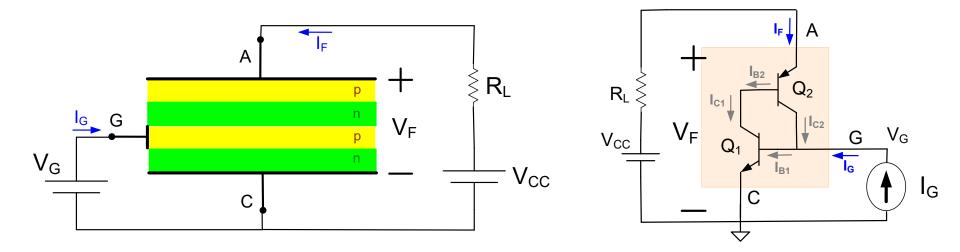

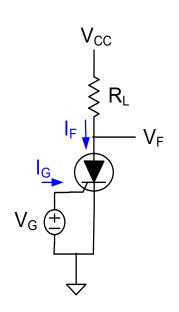

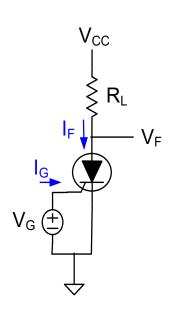

Consider a modified application by adding a load (depicted as  $R_L$ )

All operation is as before, but now, after the triggering occurs, the voltage  $V_F$  will drop to approximately 0.8 V and the voltage  $V_{CC}$ -.8 will appear across  $R_L$

If  $V_{CC}$  is very large, the SCR has effectively served as a switch putting  $V_{CC}$  across the load and after triggering occurs,  $I_G$  can be removed!

But, how can we turn it off? Will discuss that later

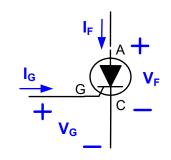

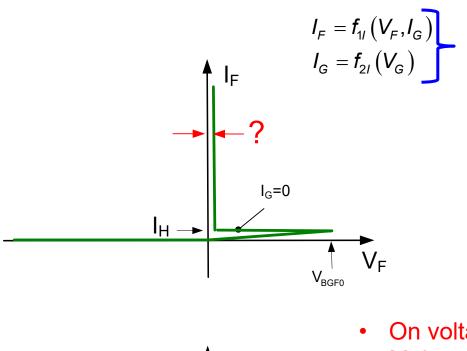

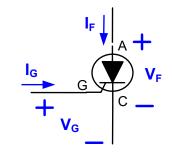

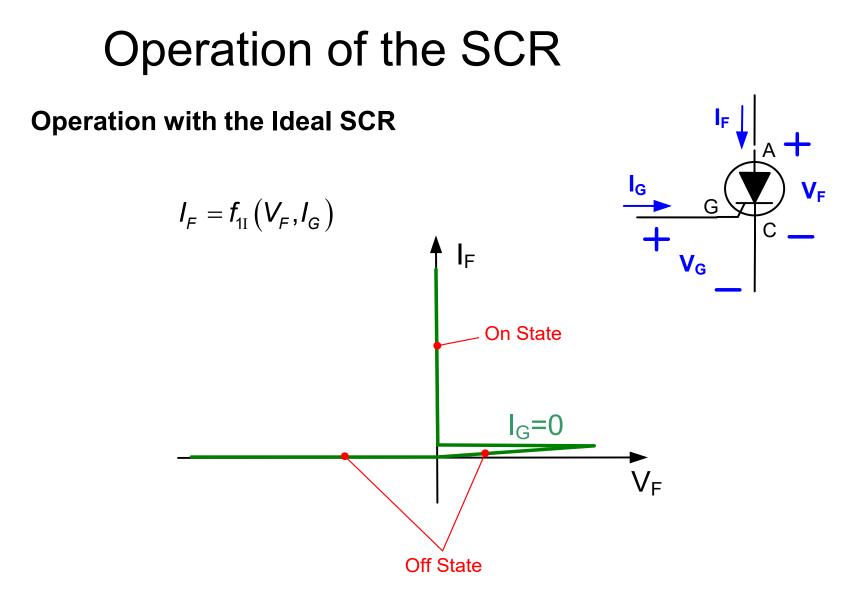

SCR model  $I_F = f_1(V_F, V_G)$  $I_G = f_2(V_G)$

As for MOSFET, Diode, and BJT, several models for SCR can be developed

The Ideal SCR Model

Consider the Ideal SCR Model

Consider the Ideal SCR Model

Consider nearly Ideal SCR Model

- On voltage approximately 0.9V

- Major contributor to ON-state power dissipation

- Even with large currents, P<sub>ON</sub> is quite small

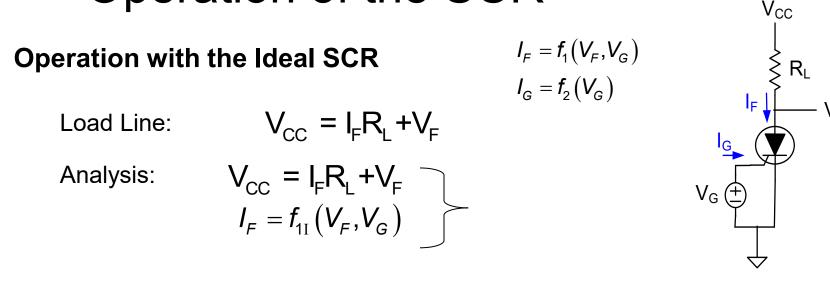

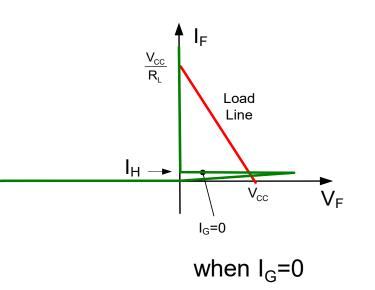

The solution of these two equations is at the intersection of the load line and the device characteristics

Note three intersection points Two (upper and lower) are stable equilibrium points, one is not

When operating at upper point,  $V_F=0$  so  $V_{CC}$  appears across  $R_L$  We say SCR is ON

When operating at lower point,  $I_F$  approx 0 so no signal across  $R_L$  We say SCR is OFF

When  $I_G=0$ , will stay in whatever state it was in

For notational convenience will drop subscript unless emphasis is needed

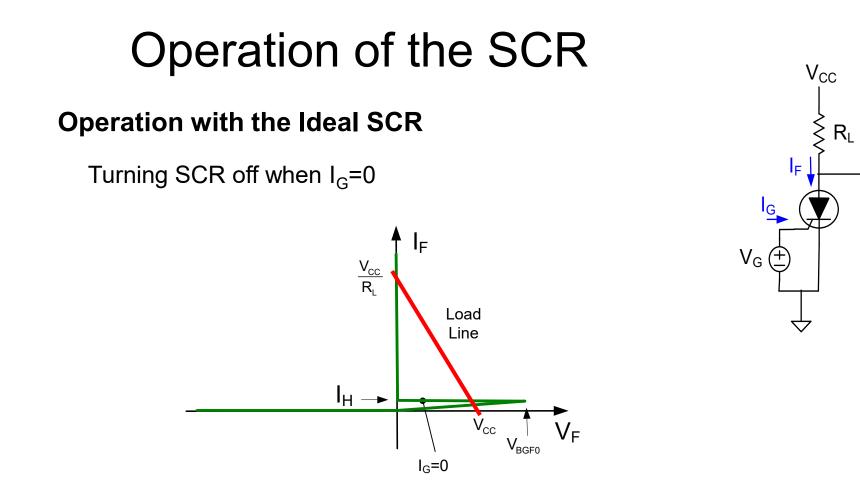

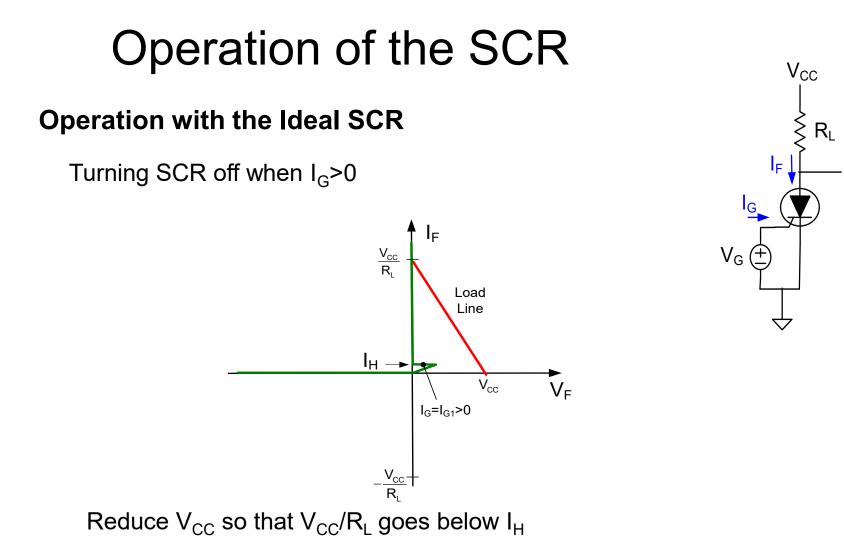

#### **Operation with the Ideal SCR**

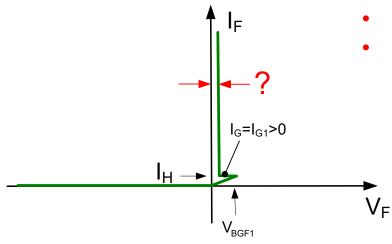

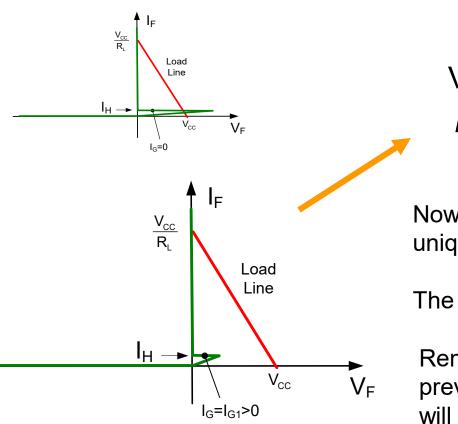

Now assume it was initially in the OFF state and then a gate current was applied

$$V_{CC} = I_F R_L + V_F$$

$$I_F = f(V_F, I_G)$$

Now there is a single intersection point so a unique solution

V<sub>CC</sub>

IF.

IG

$V_{G}$

R

VF

The SCR is now ON

Removing the gate current will return to the previous solution (which has 3 intersection points) but it will remain in the ON state

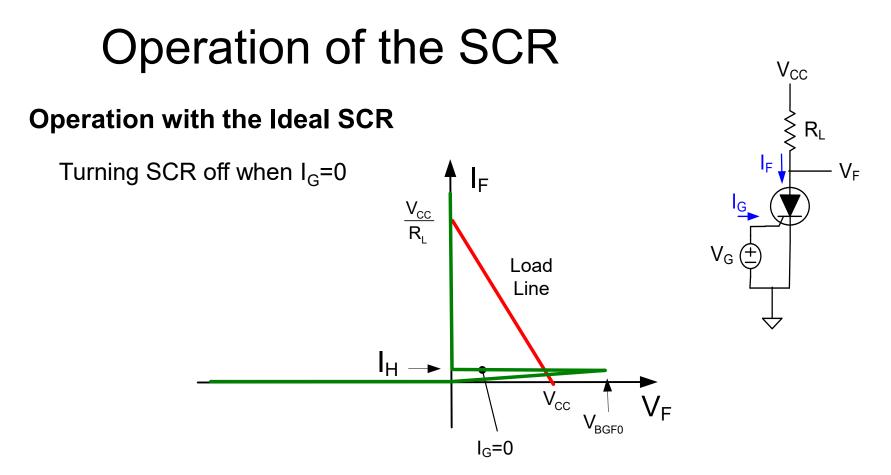

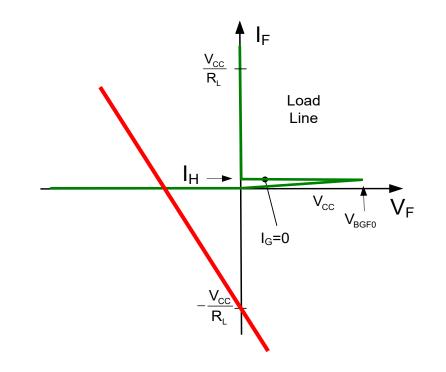

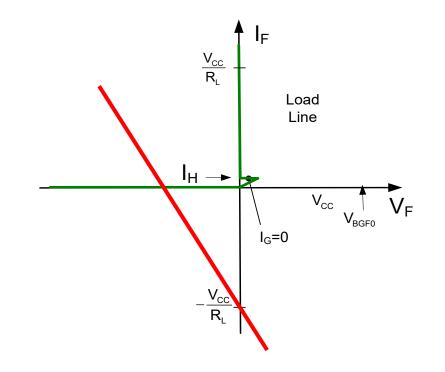

Reduce  $V_{CC}$  so that  $V_{CC}/R_L$  goes below  $I_H$

This will provide a single intersection point

$V_{\text{CC}}$  can then be increased again and SCR will stay off

Must not increase  $V_{CC}$  much above  $V_{BGF0}$  else will turn on

$V_{\mathsf{F}}$

#### **Operation with the Ideal SCR**

Often V<sub>CC</sub> is an AC signal (often 110V)

SCR will turn off whenever AC signal goes negative

#### **Operation with the Ideal SCR**

Often V<sub>CC</sub> is an AC signal (often 110V)

SCR will turn off whenever AC signal goes negative

VF

This will provide a single intersection point

But when  $V_{\text{CC}}\,$  is then increased SCR will again turn on

# Stay Safe and Stay Healthy !

# End of Lecture 29